我校信息科学与工程学院集成电路团队提出一种具有超低导通电阻的横向双扩散金属氧化物场效应晶体管(LDMOS)器件结构,在保证器件工艺兼容性的前提下,实现了击穿电压和导通电阻的同步提升,综合性能达到世界先进水平。近日,相关成果以“An Ultralow Ron,sp Accumulation LDMOS with High Process and Application Compatibility”为题发表于功率器件领域顶级期刊IEEE Electron Device Letters,论文第一单位为济南大学信息科学与工程学院、山东省泛在智能计算重点实验室(筹),李阳教授为通讯作者,张春伟为第一作者。

LDMOS具有耐压能力强、电流密度大、可集成的优点,是电源管理芯片、驱动芯片等高压集成电路不可或缺的核心元器件,对相关芯片的性能具有关键性影响,广泛应用于各类电气设备的电源系统,对我国能源转换效率和节能减排具有重要作用,其关键核心技术研究受到了学术界和产业界的广泛关注。该工作针对LDMOS的耐压能力和导通电阻两大相互制约的关键指标,提出了一种同步优化改进的设计技术。

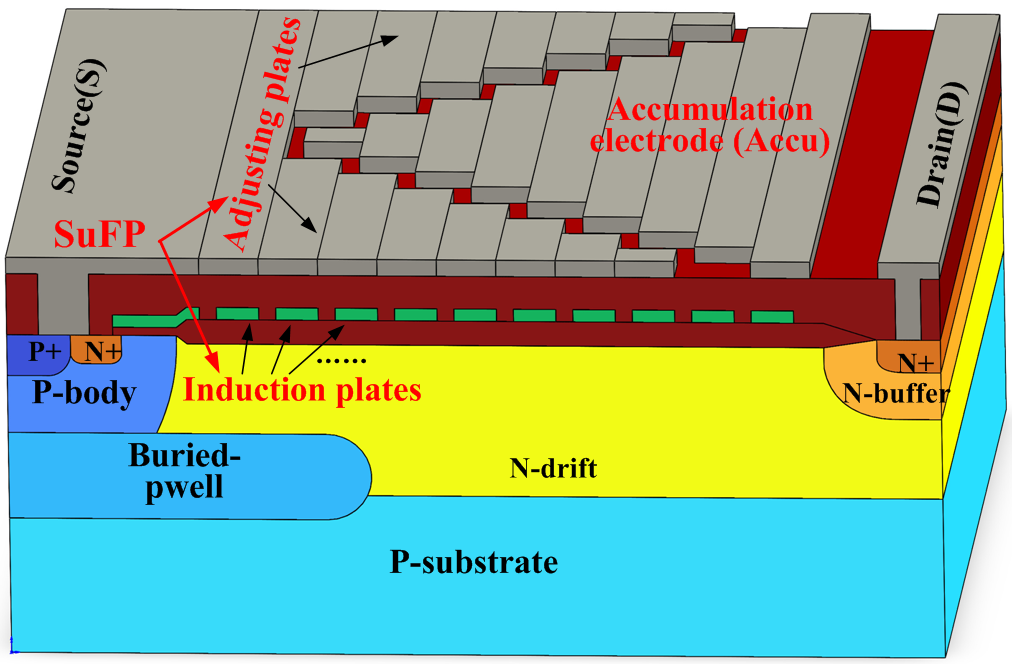

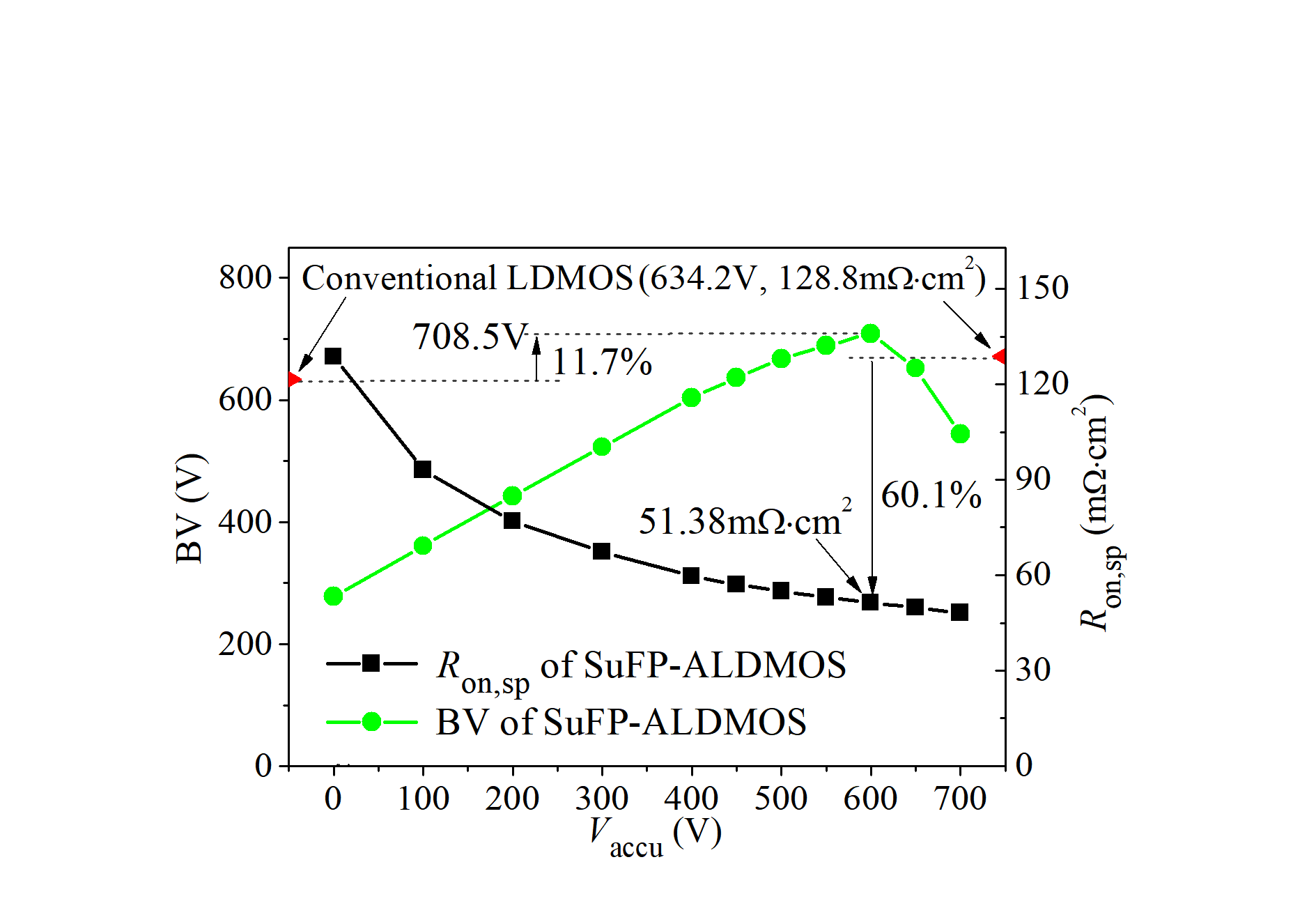

团队针对LDMOS器件漂移区掺杂浓度使器件耐压能力和导通电阻此消彼涨、无法同时提升的关键问题,提出利用感应电荷代替杂质电离电荷控制器件载流子和电场分布的策略,通过引入连接系统VDD的积累电极控制浮空感应场板,使其在器件耐压状态下感应负电荷、调制电场分布,在器件导通状态下感应正电荷、感应增加漂移区载流子浓度,从而实现器件的击穿电压和导通电阻同步提升,突破了耐压能力和导通电阻相互制约的问题。基于600V耐压等级的LDMOS实验结果显示,器件在关态下实现了均匀的电场分布,耐压能力提升11.7%,同时,器件工作于VDD= 600V系统的导通电阻降低了60.1%,器件综合性能(FOM)提升211.1%达到世界先进水平。该新型器件结构与现有制备工艺完全兼容,同时也与系统应用兼容,相比其他技术在成本和兼容性方面具有明显的优势,对未来功率器件发展具有重要推动作用。

超低导通电阻积累型LDMOS器件结构示意图

耐压能力和导通电阻测试结果

济南大学集成电路团队主要开展功率半导体器件、神经形态器件、忆阻器、柔性传感器、模拟集成电路、智能感知系统等新型器件、电路及系统研究。该工作得到了国家自然科学基金、山东省泰山学者人才工程、山东省高等学校青年创新团队等项目的支持。

撰稿:张春伟 编辑:刘孟頔 编审:张伟